1. Einleitung

Quarzoszillatoren erzeugen hochstabile Taktsignale, die in nahezu allen elektronischen Systemen benötigt werden – von einfachen Mikrocontroller-Schaltungen bis hin zu Hochgeschwindigkeits-Datenübertragungssystemen.

Das Ausgangssignal eines Oszillators muss dabei zur nachgeschalteten Logikfamilie oder Schnittstelle passen. Im Laufe der Jahrzehnte haben sich verschiedene Ausgangsstandards entwickelt, die jeweils auf die Anforderungen ihrer Zeit und Anwendung zugeschnitten sind.

Dieses Dokument gibt einen umfassenden Überblick über die sieben gängigsten Ausgangssignaltypen bei Quarzoszillatoren: CMOS, TTL, Clipped Sine Wave, Sinus, LVPECL, LVDS und HCSL.

Für jeden Typ werden die historische Entwicklung, die elektrischen Eigenschaften, die typische Signalform sowie die bevorzugten Einsatzgebiete erläutert.

2. Historische Entwicklung

Die Entwicklung der Ausgangssignaltypen lässt sich eng mit der Evolution der Halbleitertechnologie und den steigenden Anforderungen an Taktfrequenzen und Signalintegrität verknüpfen:

2.1 TTL (Transistor-Transistor-Logik) – ab ca. 1964

TTL war einer der ersten weit verbreiteten digitalen Logikstandards und wurde von Texas Instruments als 7400-Serie eingeführt. Oszillatoren mit TTL-Ausgang arbeiten mit einer Versorgungsspannung von 5 V und liefern Pegelbereiche, die direkt mit TTL-Gattern kompatibel sind. Der Standard prägte die digitale Elektronik über Jahrzehnte und war bis in die 1990er-Jahre der dominierende Logikstandard.

2.2 CMOS (Complementary Metal-Oxide-Semiconductor) – ab ca. 1968

CMOS-Technologie wurde ursprünglich von RCA entwickelt und zeichnet sich durch extrem niedrigen Ruhestromverbrauch aus. CMOS-Oszillatoren liefern Rail-to-Rail-Ausgangssignale, d. h. der Ausgang schwingt nahezu zwischen 0 V und VCC. Mit der fortschreitenden Miniaturisierung und dem Trend zu niedrigeren Versorgungsspannungen (3,3 V, 2,5 V, 1,8 V) wurde CMOS zum meistverwendeten Ausgangsstandard für Quarzoszillatoren.

2.3 Sinus – seit den Anfängen der Oszillatortechnik

Sinusförmige Ausgangssignale sind so alt wie die Oszillatortechnik selbst. Quarzoszillatoren schwingen physikalisch sinusförmig; alle anderen Signalformen werden erst durch nachgeschaltete Schaltungen erzeugt. Sinusausgänge werden bevorzugt in der Hochfrequenztechnik, bei Messgeräten und in der analogen Signalverarbeitung eingesetzt, da sie keine Oberwellen erzeugen.

2.4 Clipped Sine Wave – ab ca. 1970er-Jahre

Der Clipped-Sine-Wave-Ausgang stellt einen Kompromiss zwischen Sinus- und Rechteckausgang dar. Das Sinussignal wird dabei an den Spitzen begrenzt (geclippt), wodurch steilere Flanken als beim reinen Sinus entstehen, aber weniger Oberwellen als bei einem Rechtecksignal. Dieser Ausgangstyp fand besonders in der Telekommunikation und bei älteren Hochfrequenz-Applikationen Verwendung. Clipped-Sine-Wave-ICs werden heute hauptsächlich noch in TCXOs eingesetzt. Mit dieser Technologie lassen sich deutlich stromsparende TCXOs als wie mit der CMOS-Technologie aufbauen. CSW-TCXOs werden deshalb als Referenz in Navigationsgeräten, Notrufsystemen, Gateways eingesetzt. Überall da, wo man Signalreichweite (Funk) und eine hochgenaue Positionierung benötigt.

2.5 LVPECL (Low-Voltage Positive Emitter-Coupled Logic) – ab ca. 1990er-Jahre

Mit dem Bedarf an immer höheren Taktfrequenzen in Netzwerk- und Telekommunikationssystemen entstand LVPECL als schnelle differentielle Ausgangslogik. LVPECL basiert auf der klassischen ECL-Technik (Emitter-Coupled Logic), die bereits in den 1960er-Jahren für Hochgeschwindigkeitsanwendungen entwickelt wurde, und adaptiert diese für niedrigere Versorgungsspannungen (3,3 V statt -5,2 V). LVPECL bietet extrem kurze Schaltzeiten und ist für Frequenzen bis weit über 1 GHz geeignet.

2.6 LVDS (Low-Voltage Differential Signaling) – ab 1994

LVDS wurde 1994 als ANSI/TIA/EIA-644-Standard eingeführt und optimiert die differentielle Signalübertragung für niedrigen Stromverbrauch und hohe Datenraten. Der geringe differentielle Spannungshub von nur 350 mV ermöglicht schnelle Schaltvorgänge bei minimaler elektromagnetischer Abstrahlung. LVDS ist heute weit verbreitet in Display-Schnittstellen, seriellen Datenlinks und FPGA-Clocking.

2.7 HCSL (High-Speed Current Steering Logic) – ab ca. 2002

HCSL wurde speziell für den PCI-Express-Standard entwickelt und ist seit der ersten PCIe-Generation der Referenz-Taktstandard. Die PCI-SIG spezifizierte HCSL als strommodenbasiertes differentielles Signal mit sehr niedrigem Spannungshub, optimiert für die 100-MHz-Referenztakte in PCIe-Systemen. HCSL ist heute unverzichtbar in jedem PC, Server und Embedded-System mit PCIe-Schnittstelle.

3. Signalformen im Überblick

Die folgenden Diagramme zeigen die idealisierten Signalverläufe der sieben Ausgangstypen. Beachten Sie die unterschiedlichen Spannungsbereiche und Schwinghubs – diese sind entscheidend für die Kompatibilität mit nachgeschalteten Empfängern.

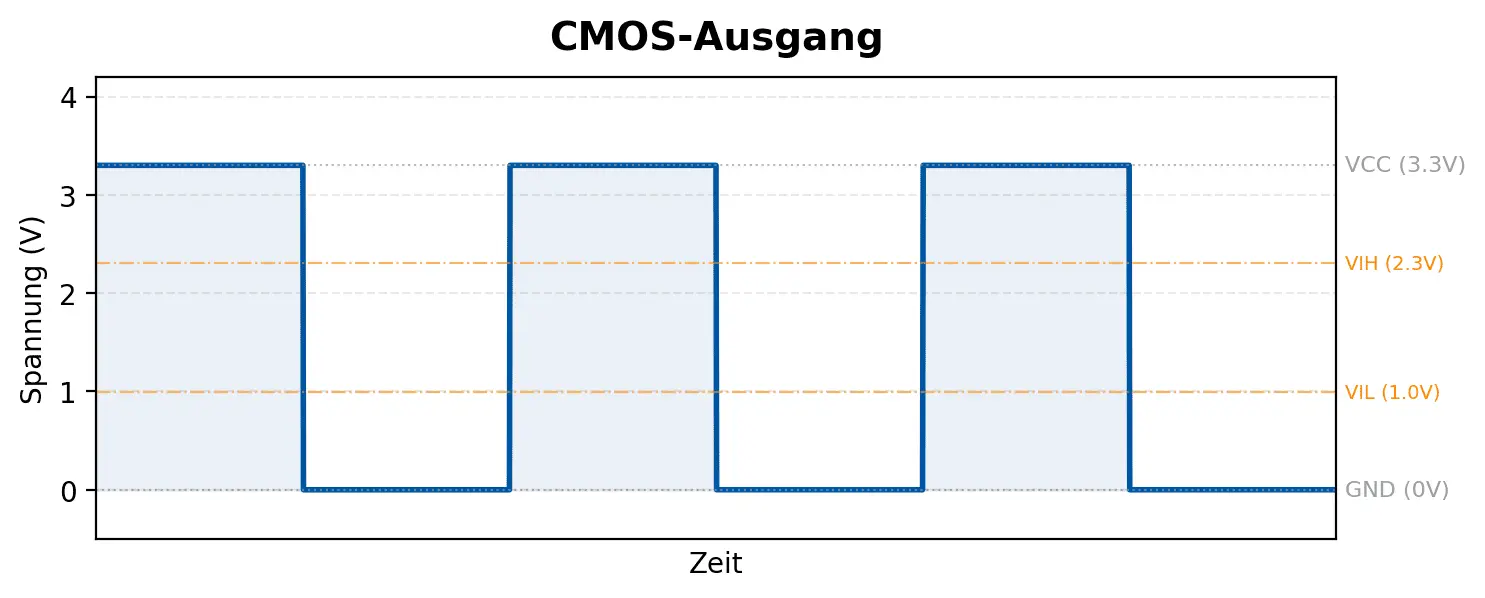

3.1 CMOS

Abb. 1: CMOS-Ausgangssignal – Rail-to-Rail-Rechteck zwischen 0 V und VCC (hier 3,3 V)

Das CMOS-Signal zeichnet sich durch seinen vollständigen Spannungshub zwischen GND und VCC aus. Die Eingangsschwellen VIL und VIH liegen typischerweise bei 30 % bzw. 70 % von VCC, was einen breiten Störabstand gewährleistet. Die symmetrischen Ausgangstreiberstrukturen (P-Kanal/N-Kanal-MOSFET) ermöglichen nahezu gleiche Anstiegs- und Abfallzeiten.

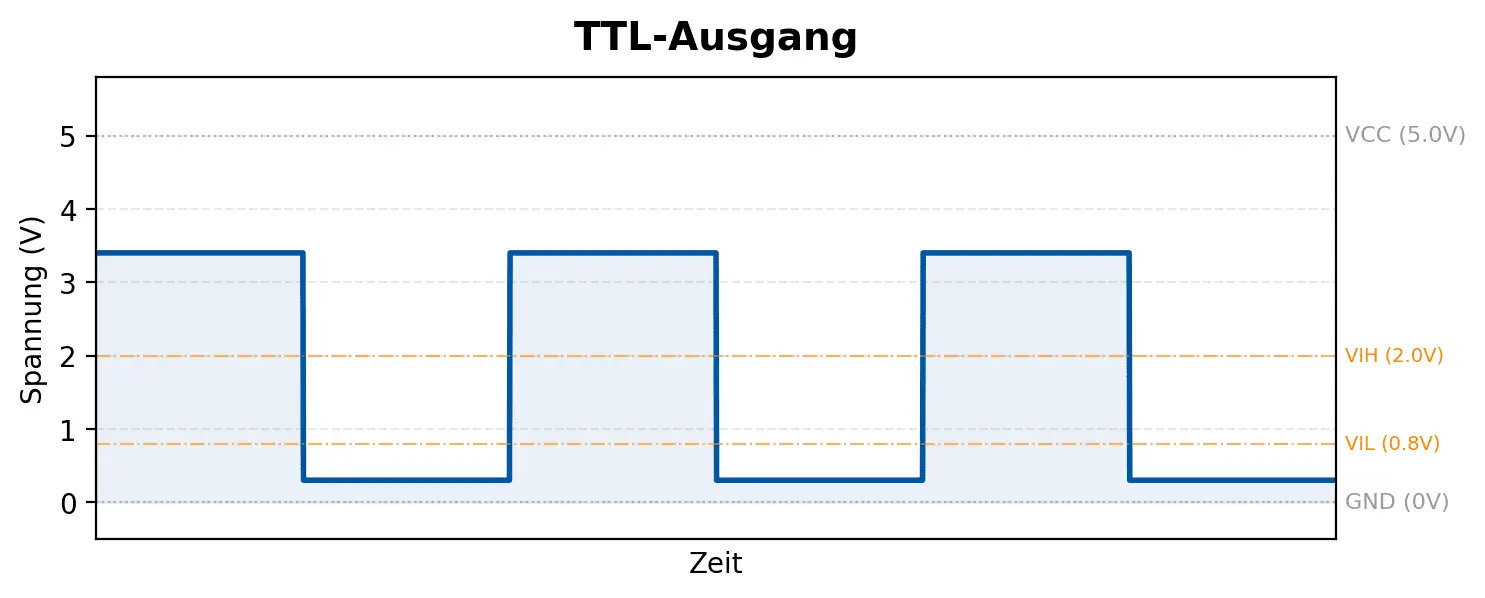

3.2 TTL

Abb. 2: TTL-Ausgangssignal – VOH typisch 3,4 V, VOL typisch 0,3 V bei 5 V Versorgung

Im Gegensatz zum CMOS-Ausgang erreicht TTL keine Rail-to-Rail-Pegel. Der High-Pegel (VOH) liegt typisch bei 3,4 V (mindestens 2,4 V), der Low-Pegel (VOL) bei maximal 0,4 V. Die asymmetrischen Schwellen (VIL = 0,8 V, VIH = 2,0 V) ergeben sich aus der bipolaren Transistorarchitektur. Der sogenannte „verbotene Bereich“ zwischen 0,8 V und 2,0 V darf im statischen Betrieb nicht angenommen werden.

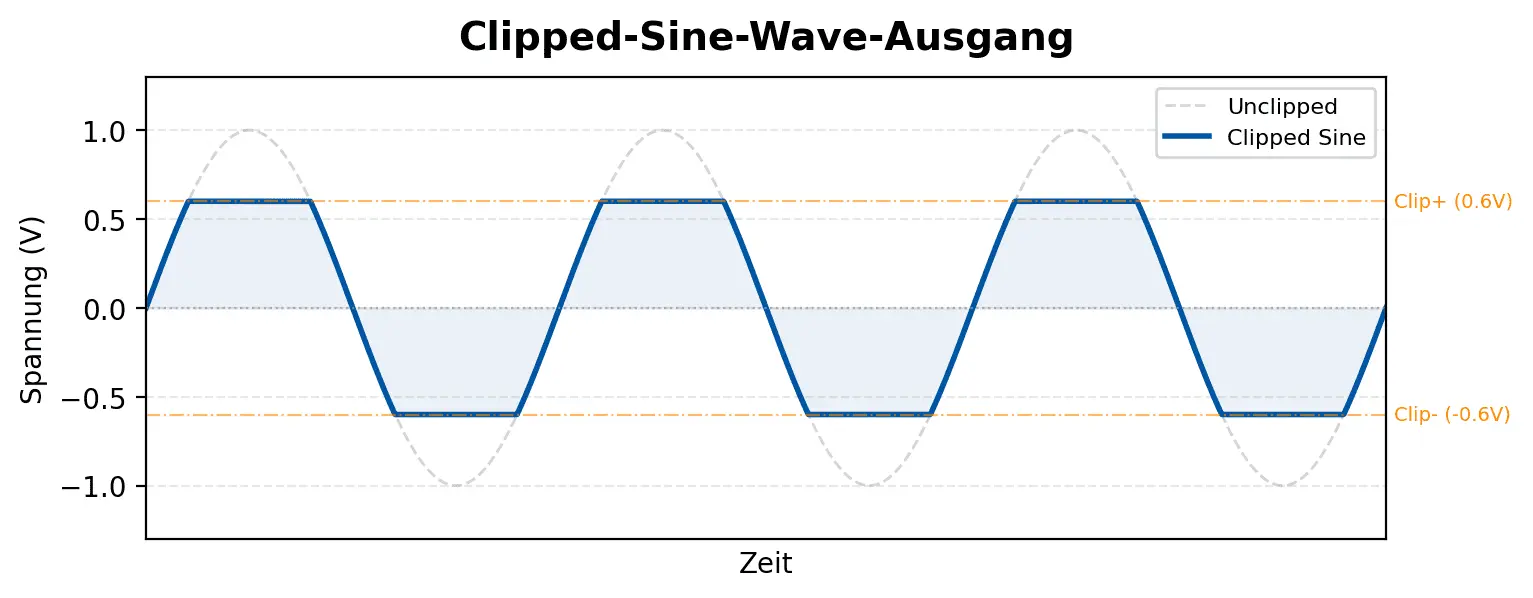

3.3 Clipped Sine Wave

Abb. 3: Clipped-Sine-Wave-Ausgang – Sinussignal mit begrenzten Amplitudenspitzen

Beim Clipped-Sine-Wave-Ausgang wird das natürliche Sinussignal des Quarzresonators an definierten Schwellwerten begrenzt. Die gestrichelte Linie zeigt den unverstümmelten Sinusverlauf. Durch das Clipping entstehen steilere Nulldurchgänge als beim reinen Sinus, was die Ansteuerung nachfolgender Logik erleichtert, während der Oberwellengehalt moderat bleibt.

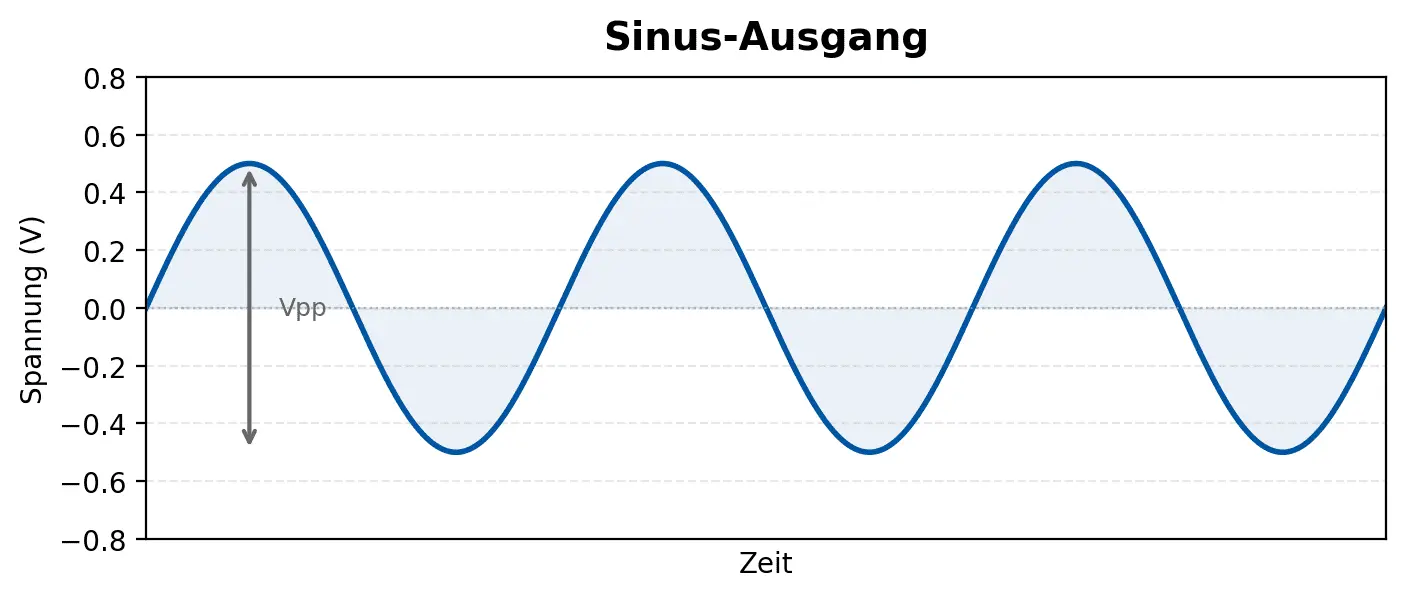

3.4 Sinus

Abb. 4: Sinus-Ausgang – Reines Sinussignal mit definierter Spitze-Spitze-Spannung (Vpp)

Der Sinusausgang liefert das sauberste Spektrum aller Ausgangsformen: idealerweise nur eine einzige Spektrallinie bei der Grundfrequenz. Die Amplitude wird als Spitze-Spitze-Spannung (Vpp) oder als Leistung in dBm angegeben. Typische Werte liegen bei 0,5 bis 1,0 Vpp oder 0 bis +13 dBm in 50-Ω-Systemen.

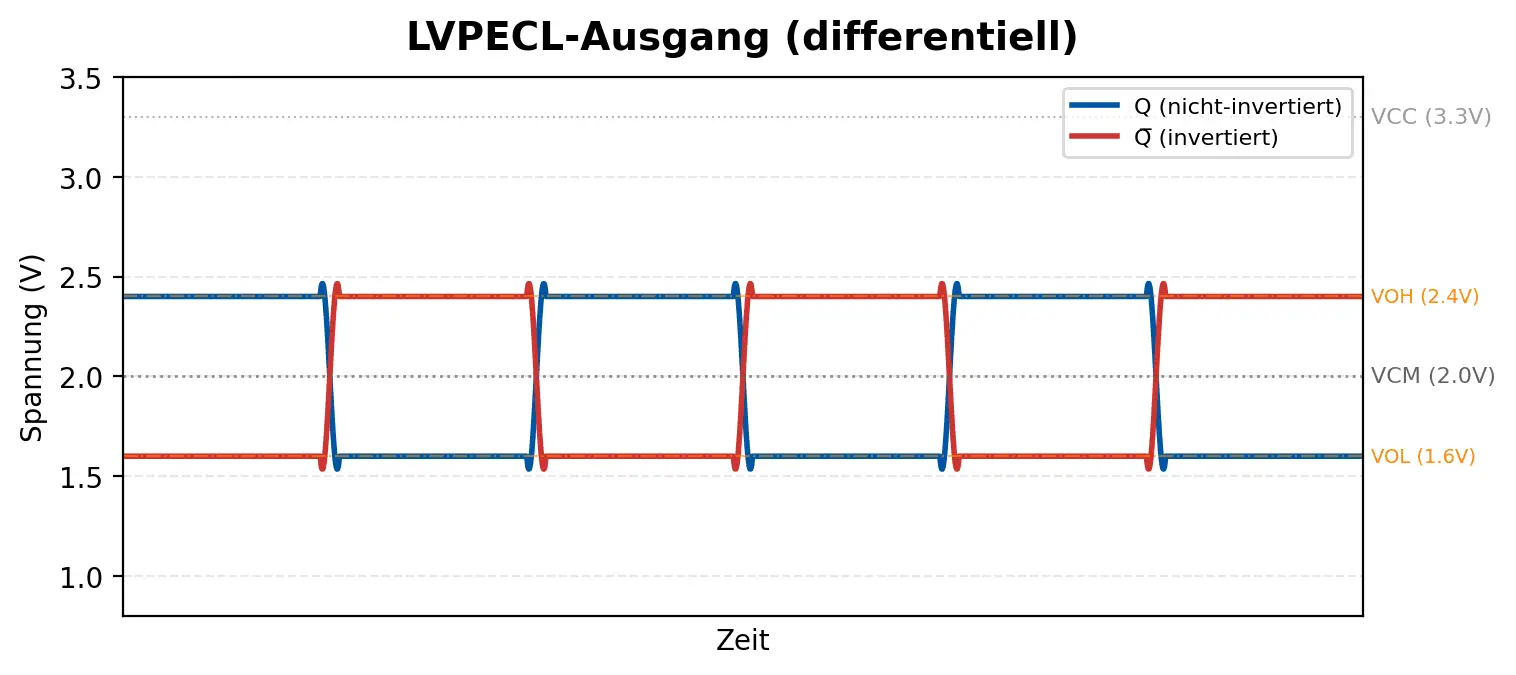

3.5 LVPECL

Abb. 5: LVPECL-Ausgang – Differentielles Signal mit ca. 800 mV Gesamthub um VCC–1,3 V

LVPECL verwendet differentielle Signalführung: Zwei komplementäre Ausgänge (Q und Q̅) schwingen gegenphasig um einen gemeinsamen Gleichtaktpegel (VCM), der typisch bei VCC–1,3 V liegt. Der differentielle Spannungshub beträgt ca. 800 mV. Die Stromquellenarchitektur ermöglicht extrem schnelle Schaltzeiten mit minimaler Überschwingneigung.

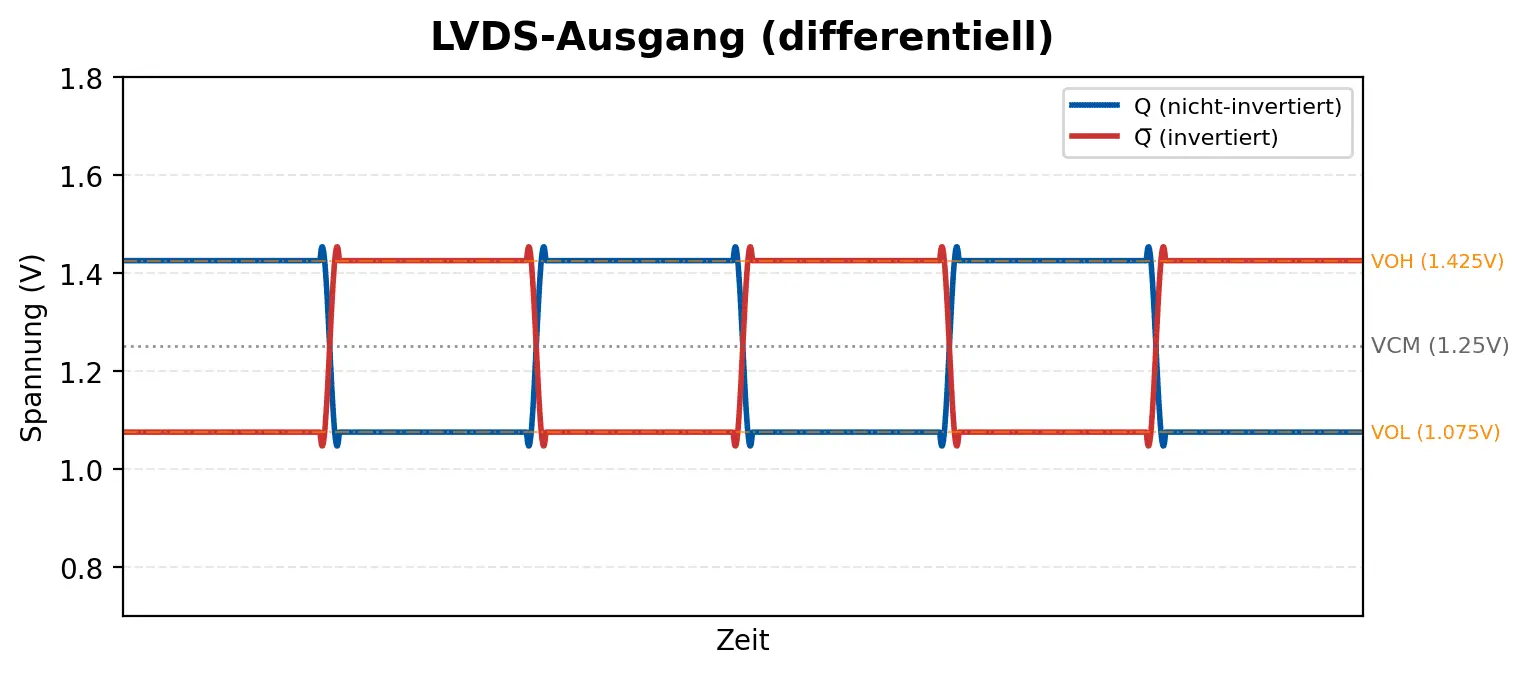

3.6 LVDS

Abb. 6: LVDS-Ausgang – Differentielles Signal mit nur 350 mV Hub um 1,25 V Gleichtaktpegel

LVDS zeichnet sich durch seinen besonders niedrigen differentiellen Spannungshub von nur 350 mV aus. Der Gleichtaktpegel liegt bei 1,25 V. Durch den stromgesteuerten Treiber (typisch 3,5 mA) und die 100-Ω-Abschlussterminierung wird eine hohe Signalintegrität bei minimalem Stromverbrauch erreicht. Die niedrige Amplitude minimiert elektromagnetische Abstrahlung.

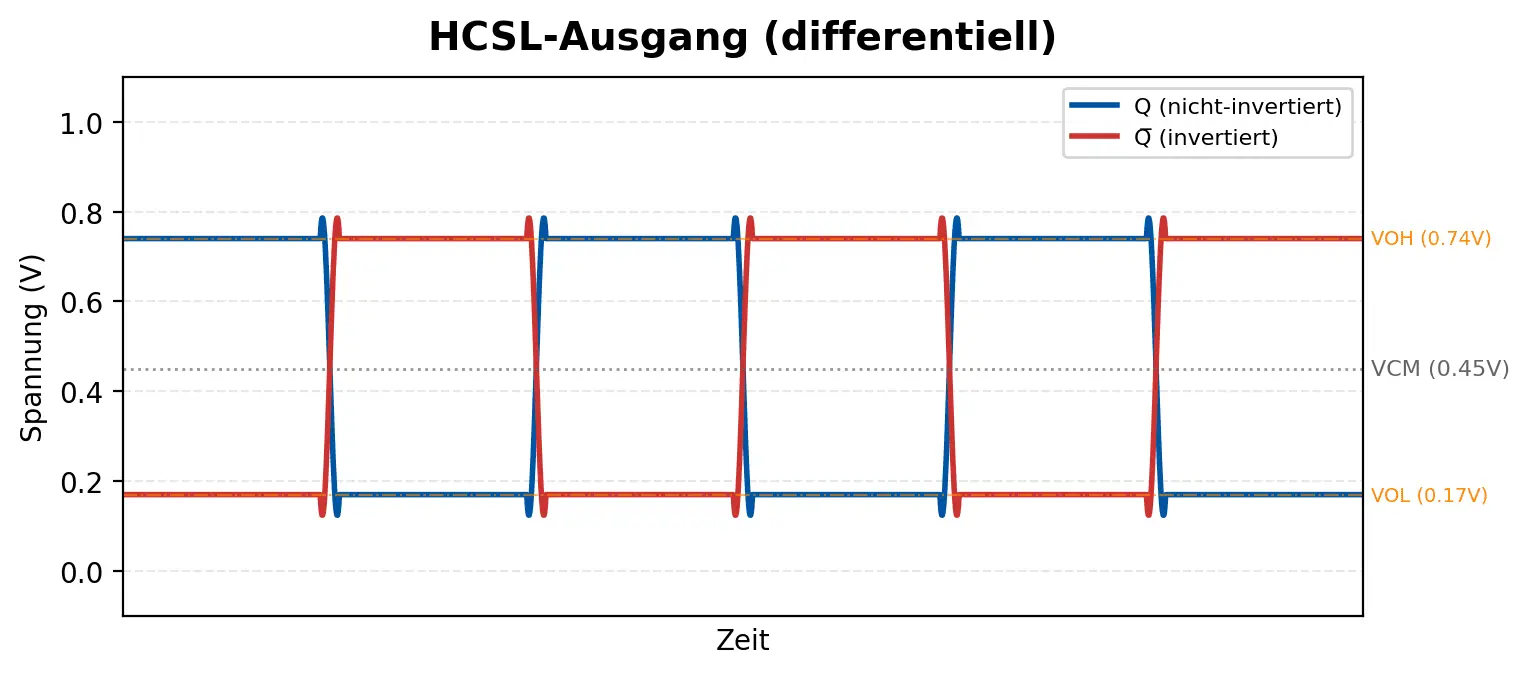

3.7 HCSL

Abb. 7: HCSL-Ausgang – Strommodenbasiertes differentielles Signal für PCIe-Referenztakte

HCSL arbeitet mit einem sehr niedrigen Spannungshub: VOH liegt typisch bei 0,74 V und VOL bei 0,17 V, woraus ein Gleichtaktpegel von ca. 0,45 V resultiert. Die Stromsteuerungsarchitektur ist speziell für die Anforderungen der PCIe-Spezifikation optimiert und erlaubt eine präzise Impedanzanpassung über 50-Ω-Terminierungen gegen Masse.

4. Vergleich der Ausgangssignale

Die folgende Tabelle fasst die wesentlichen Eigenschaften aller sieben Ausgangstypen zusammen:

Typ | Signalart | VCC (V) | VOH/ VOL (V) | Diff. Hub | Max. ca. Freq. | Typische Anwendung |

| CMOS | Single- Ended | 1,8–5,0 | VCC/ 0 | – | ~285 MHz | Mikrocontroller, FPGAs, allgemeine Digitaltechnik |

| TTL | Single- Ended | 1,8-5,0 | 3,4/ 0,3 | – | ~150 MHz | Legacy-Systeme, industrielle Steuerungen |

| Clipped Sine | Single- Ended | 1,8/2,5/3,3 | variabel | – | ~200 MHz | Telekommunikation, HF-Anwendungen |

| Sinus | Single- Ended | 3,3/5,0/12 | variabel | – | >1 GHz | HF-Technik, Messgeräte, Frequenzsynthese |

| LVPECL | Differ entiell | 2,5/3,3 | ~2,4/ ~1,6 | ~800 mV | >3 GHz | Netzwerk-Equipment, SONET/SDH, Highspeed-Clocking |

| LVDS | Differ entiell | 2,5/3,3 | ~1,43/ ~1,07 | 350 mV | >1 GHz | Display-Interfaces, serielle Links, FPGA-Clocking |

| HCSL | Differ entiell | 3,3 | 0,74/ 0,17 | ~570 mV | ~200 MHz | PCI Express Referenztakt (100 MHz) |

5. Wesentliche Unterschiede im Detail

5.1 Single-Ended vs. Differentiell

Der fundamentalste Unterschied zwischen den Ausgangstypen ist die Signalführung. CMOS, TTL, Clipped Sine Wave und Sinus sind Single-Ended-Signale – sie referenzieren auf eine gemeinsame Masse. LVPECL, LVDS und HCSL hingegen sind differentielle Signale mit zwei komplementären Leitungen. Differentielle Signale bieten entscheidende Vorteile bei höheren Frequenzen: Sie unterdrücken Gleichtaktstörungen, ermöglichen kleinere Spannungshübe und erlauben dadurch schnellere Schaltzeiten bei geringerer elektromagnetischer Abstrahlung.

5.2 Spannungshub und Störabstand

CMOS bietet mit seinem Rail-to-Rail-Ausgang den größten absoluten Spannungshub und damit den besten statischen Störabstand. TTL hat durch die asymmetrischen Pegel einen eingeschränkteren Störabstand. Die differentiellen Standards (LVPECL, LVDS, HCSL) kompensieren ihre kleineren Spannungshübe durch die Gleichtaktunterdrückung der differentiellen Übertragung, wodurch sie in gestörten Umgebungen oft zuverlässiger arbeiten als Single-Ended-Signale.

5.3 Stromverbrauch

CMOS-Oszillatoren verbrauchen im statischen Zustand nahezu keinen Strom; der Verbrauch steigt proportional zur Frequenz (dynamische Verlustleistung). TTL hat einen konstant höheren Ruhestromverbrauch aufgrund der bipolaren Architektur. LVPECL benötigt externe Abschlusswiderstände und hat den höchsten Stromverbrauch der differentiellen Standards. LVDS ist für seinen niedrigen Stromverbrauch bekannt (typisch 3,5 mA Treiberstrom). HCSL liegt hinsichtlich des Stromverbrauchs zwischen LVDS und LVPECL.

5.4 Frequenzbereich und Anwendungsschwerpunkte

Für Frequenzen bis etwa 200 MHz sind CMOS-Oszillatoren in den meisten Fällen die erste Wahl aufgrund ihrer Vielseitigkeit, des einfachen Schaltungsdesigns und der breiten Verfügbarkeit. Ab etwa 200 MHz empfehlen sich differentielle Ausgänge. LVPECL bietet die höchsten Frequenzen (>3 GHz) und wird in Netzwerk- und Telekommunikationsequipment eingesetzt. LVDS deckt einen breiten Mittelbereich ab und ist besonders in FPGA- und Display-Anwendungen verbreitet. HCSL ist auf seinen Nischenanwendungsfall optimiert: den 100-MHz-Referenztakt für PCI Express.

5.5 Terminierung und Schaltungsaufwand

CMOS- und TTL-Ausgänge benötigen in der Regel keine externe Terminierung bei kurzen Leitungslängen – dies macht sie besonders einfach in der Anwendung. LVPECL erfordert zwingend externe Abschlusswiderstände (typisch: Thevenin-Terminierung gegen VCC–2 V oder Widerstände gegen Masse), was den Schaltungsaufwand erhöht. LVDS wird standardmäßig mit einem 100-Ω-Differentialwiderstand am Empfänger terminiert. HCSL nutzt 50-Ω-Widerstände gegen Masse an jedem Ausgang.

6. Überschwinger bei Oszillator-Ausgangssignalen

6.1 Was sind Überschwinger?

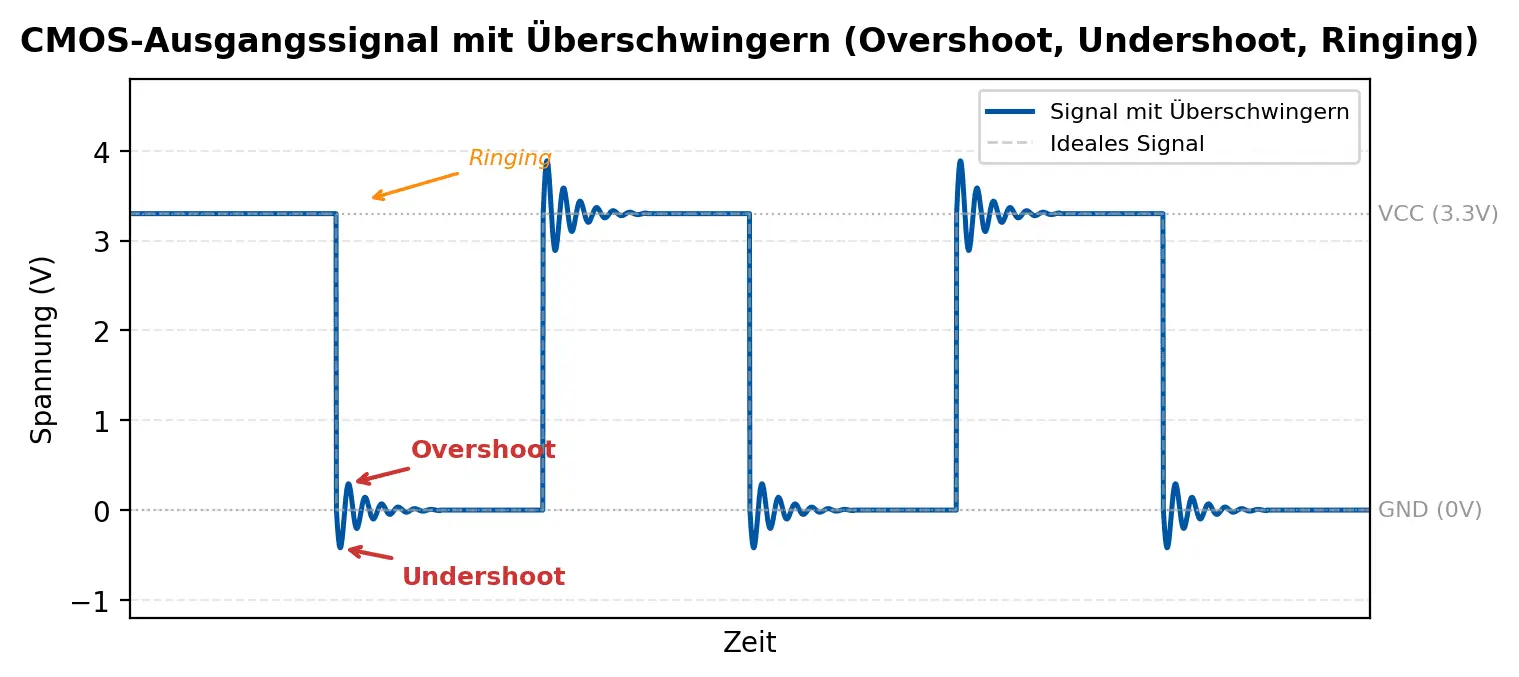

Überschwinger (englisch: Overshoot und Undershoot) sind kurzzeitige Spannungsspitzen, die bei schnellen Schaltvorgängen auftreten. Bei einer steigenden Flanke schießt die Spannung kurz über VCC hinaus (Overshoot), bei einer fallenden Flanke kurz unter GND (Undershoot). Oft folgen darauf gedämpfte Oszillationen, die als „Ringing“ bezeichnet werden.

Die Ursache liegt in der Kombination aus den sehr steilen Schaltflanken des Ausgangstreibers und den parasitären Induktivitäten und Kapazitäten der Leiterbahn, des Gehäuses und der Lastkapazität. Physikalisch betrachtet entsteht ein Schwingkreis aus der Leitungsinduktivität und der Eingangskapazität des Empfängers. Je steiler die Schaltflanke und je länger die Leiterbahn, desto ausgeprägter das Überschwingen.

Abb. 8: CMOS-Ausgangssignal mit Überschwingern – Overshoot über VCC, Undershoot unter GND und nachfolgendes Ringing

6.2 Warum sind Überschwinger problematisch?

Überschwinger, die über VCC oder unter GND gehen, können die ESD-Schutzdioden des Empfänger-ICs in Durchlassrichtung treiben und so parasitäre Ströme erzeugen. Im schlimmsten Fall kann dies zu einem Latch-up führen – einem unkontrollierten Stromfluss durch parasitäre Thyristorstrukturen im CMOS-IC, der das Bauteil zerstören kann. Starkes Ringing kann außerdem Mehrfachtriggerung an Takteingrängen verursachen, wenn die Spannung die Schaltschwelle mehrfach kreuzt, was zu fehlerhaftem Systemverhalten führt.

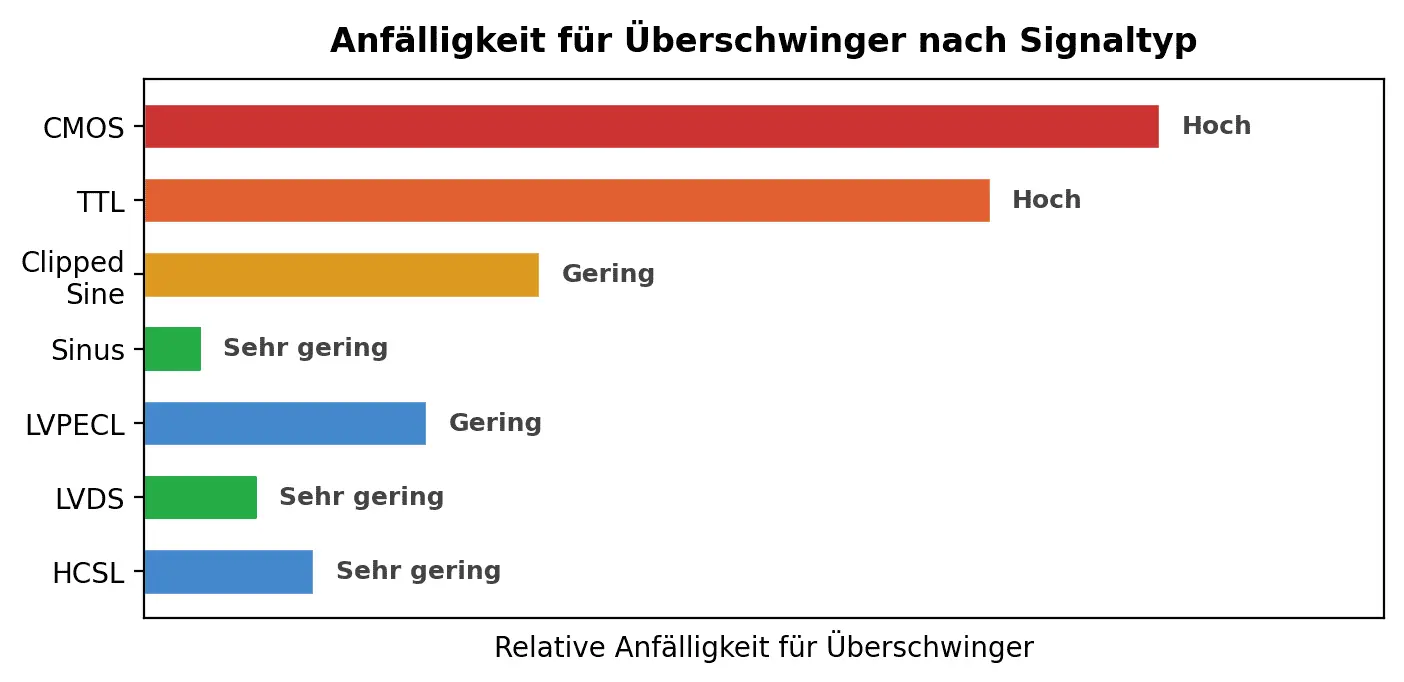

6.3 Gegenüberstellung: Überschwinger nach Signaltyp

Die Anfälligkeit für Überschwinger unterscheidet sich erheblich zwischen den verschiedenen Ausgangstypen. Die folgende Grafik zeigt die relative Anfälligkeit im Vergleich:

6.4 Überschwinger bei Single-Ended-Signalen

CMOS: Am stärksten betroffen. Die symmetrischen P-/N-Kanal-MOSFET-Treiber erzeugen sehr steile Flanken, die in Kombination mit Leitungsinduktivitäten ausgeprägte Überschwinger verursachen. Besonders bei modernen Low-Voltage-CMOS-Oszillatoren (1,8 V) können die Überschwinger relativ zur Versorgungsspannung signifikant sein.

TTL: Ebenfalls anfällig, allerdings aus etwas anderen Gründen. Die asymmetrische Totem-Pole-Ausgangsstufe erzeugt bei der steigenden Flanke einen kurzen Stromspike, wenn beide Transistoren gleichzeitig leitend sind (Cross-Conduction). Die typischerweise etwas langsameren Flanken gegenüber modernem CMOS entschärfen das Problem leicht.

Clipped Sine Wave: Deutlich weniger anfällig. Durch die begrenzten Amplitudenspitzen und die vergleichsweise weichen Flanken entsteht wesentlich weniger hochfrequente Energie, die Reflexionen und Ringing anregen könnte. Das Clipping wirkt wie eine natürliche Amplitudenbegrenzung, die Überschwinger bereits im Signal unterdrückt.

Sinus: Praktisch immun gegen klassische Überschwinger. Da das Signal keine abrupten Flankenübergänge enthält, wird kein breitbandiger Energieimpuls erzeugt, der Leitungsresonanzen anregen könnte. Bei Impedanzfehlanpassungen können allerdings stehende Wellen und Reflexionen auftreten, die die Signalamplitude an bestimmten Punkten verändern. Dies wird über klassische HF-Terminierung (50 Ω oder 75 Ω Abschluss) kontrolliert.

6.5 Überschwinger bei differentiellen Signalen

LVPECL: Dank der Stromquellenausgangsstufe inhärent gut unterdrückt. Die Stromsteuerung begrenzt die maximale Flankensteilheit auf natürliche Weise. Bei unzureichender Terminierung können dennoch Reflexionen auftreten, da LVPECL mit sehr hohen Frequenzen arbeitet. Die korrekte Thevenin- oder Emitterfolgerschaltung ist hier entscheidend – nicht primär wegen Überschwingern, sondern um den korrekten Arbeitspunkt sicherzustellen und Reflexionen zu vermeiden.

LVDS: Konstruktionsbedingt sehr robust. Der stromgesteuerte Treiber liefert einen konstanten Strom von typisch 3,5 mA in die 100-Ω-Differentialterminierung, wodurch der Spannungshub physikalisch begrenzt wird. Selbst bei Impedanzdiskontinuitäten bleiben Reflexionen klein, da der geringe Spannungshub von nur 350 mV wenig Energie für Störungen bereitstellt. LVDS ist einer der gutmütigsten Standards hinsichtlich Signalintegrität.

HCSL: Verhält sich ähnlich wie LVDS durch die strombasierte Architektur. Der sehr niedrige Spannungshub und die 50-Ω-Terminierung gegen Masse sorgen für saubere Impedanzanpassung. In der PCIe-Spezifikation sind die zulässigen Überschwinger explizit definiert und eng toleriert, sodass HCSL-konforme Oszillatoren diese Anforderungen bereits von Haus aus einhalten.

6.6 Gegenmaßnahmen zur Kontrolle von Überschwingern

Die wirksamste Maßnahme bei Single-Ended-Signalen (insbesondere CMOS und TTL) ist ein Seriewiderstand direkt am Ausgang des Oszillators, typischerweise im Bereich von 22 bis 47 Ω. Dieser Widerstand bildet zusammen mit der Leitungsimpedanz einen Spannungsteiler, der die Flanke dämpft und Reflexionen absorbiert. Der optimale Wert ergibt sich aus der Differenz zwischen Leitungsimpedanz und Ausgangsimpedanz des Treibers.

Darüber hinaus helfen kurze, impedanzkontrollierte Leiterbahnen, die Minimierung von Durchkontaktierungen (Vias) auf der Taktleitung, eine durchgehende Massefläche unter der Signalleitung sowie ausreichende Entkoppelkondensatoren nahe am Oszillator (typisch 100 nF keramisch plus 10 µF). Manche CMOS-Oszillator-Hersteller bieten zudem Modelle mit kontrollierter Flankensteilheit (Slew Rate Control) an, die das Problem bereits im Treiber entschärfen.

Bei differentiellen Signalen (LVPECL, LVDS, HCSL) ist die korrekte, spezifikationskonforme Terminierung die wichtigste Maßnahme. Zusätzlich sollten die beiden Leitungen eines differentiellen Paares stets längengleich und eng gekoppelt geführt werden, um Skew (Laufzeitunterschiede) zu minimieren und die Gleichtaktunterdrückung zu erhalten.

7. Entscheidungshilfe

Die Wahl des richtigen Ausgangstyps hängt im Wesentlichen von vier Faktoren ab: der erforderlichen Taktfrequenz, der Logikfamilie des Empfängers, dem verfügbaren Leistungsbudget und den Anforderungen an die Signalintegrität.

Anwendungsfall | Empfehlung |

| Allgemeine Digitaltechnik, µC, FPGA-I/O (bis ~200 MHz) | CMOS – Einfachste und günstigste Lösung, Rail-to-Rail, breiteste Verfügbarkeit, flexibel bei der Versorgungsspannung (1,8–5,0 V) |

| Legacy-5V-Systeme, industrielle Steuerungen | TTL – Direkt kompatibel zu älteren 5V-Logikfamilien; wird zunehmend durch CMOS mit 5V-Versorgung ersetzt |

| HF-Anwendungen, über- tragerbasierte Schaltungen | Clipped Sine Wave oder Sinus – Geringerer Oberwellengehalt reduziert EMV-Probleme und ermöglicht präzise Frequenzsynthese |

| Hochgeschwindigkeits-Netzwerk- equipment (>622 MHz) | LVPECL – Höchste Schaltgeschwindigkeit, ideal für SONET/SDH, Ethernet-PHYs und Backplane-Takte |

| FPGA-Clocking, serielle Daten-übertragung, Display-Interfaces | LVDS – Optimaler Kompromiss aus Geschwindigkeit, Stromverbrauch und EMV-Verhalten |

| PCI Express Referenztakt | HCSL – Einziger von der PCI-SIG spezifizierter Taktstandard für PCIe-Systeme |